ESP32: Difference between revisions

| (47 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

=Introduction= | =Introduction= | ||

As the little grey cells get older probably time to give to pointers to myself | As the little grey cells get older probably time to give to pointers to myself | ||

=Arduino= | |||

Installation on ubuntu is | |||

<syntaxhighlight lang="bash"> | |||

sudo snap install arduino | |||

</syntaxhighlight> | |||

The important step is to address for the board configuration | |||

<syntaxhighlight lang="bash"> | |||

https://dl.espressif.com/dl/package_esp32_index.json | |||

</syntaxhighlight> | |||

This can be install by following steps on https://randomnerdtutorials.com/installing-the-esp32-board-in-arduino-ide-windows-instructions/ | |||

=UDev Rules= | =UDev Rules= | ||

Here is what I use for my WROOM 32d in /etc/udev/rules.d/98-esp32.rules | Here is what I use for my WROOM 32d in /etc/udev/rules.d/98-esp32.rules | ||

| Line 10: | Line 21: | ||

sudo usermod -a -G dialout $USER | sudo usermod -a -G dialout $USER | ||

</syntaxhighlight> | </syntaxhighlight> | ||

=Building openocd= | =Building openocd= | ||

This is a cop out as I should fix the errors and feed back but here we go. | This is a cop out as I should fix the errors and feed back but here we go. | ||

| Line 19: | Line 31: | ||

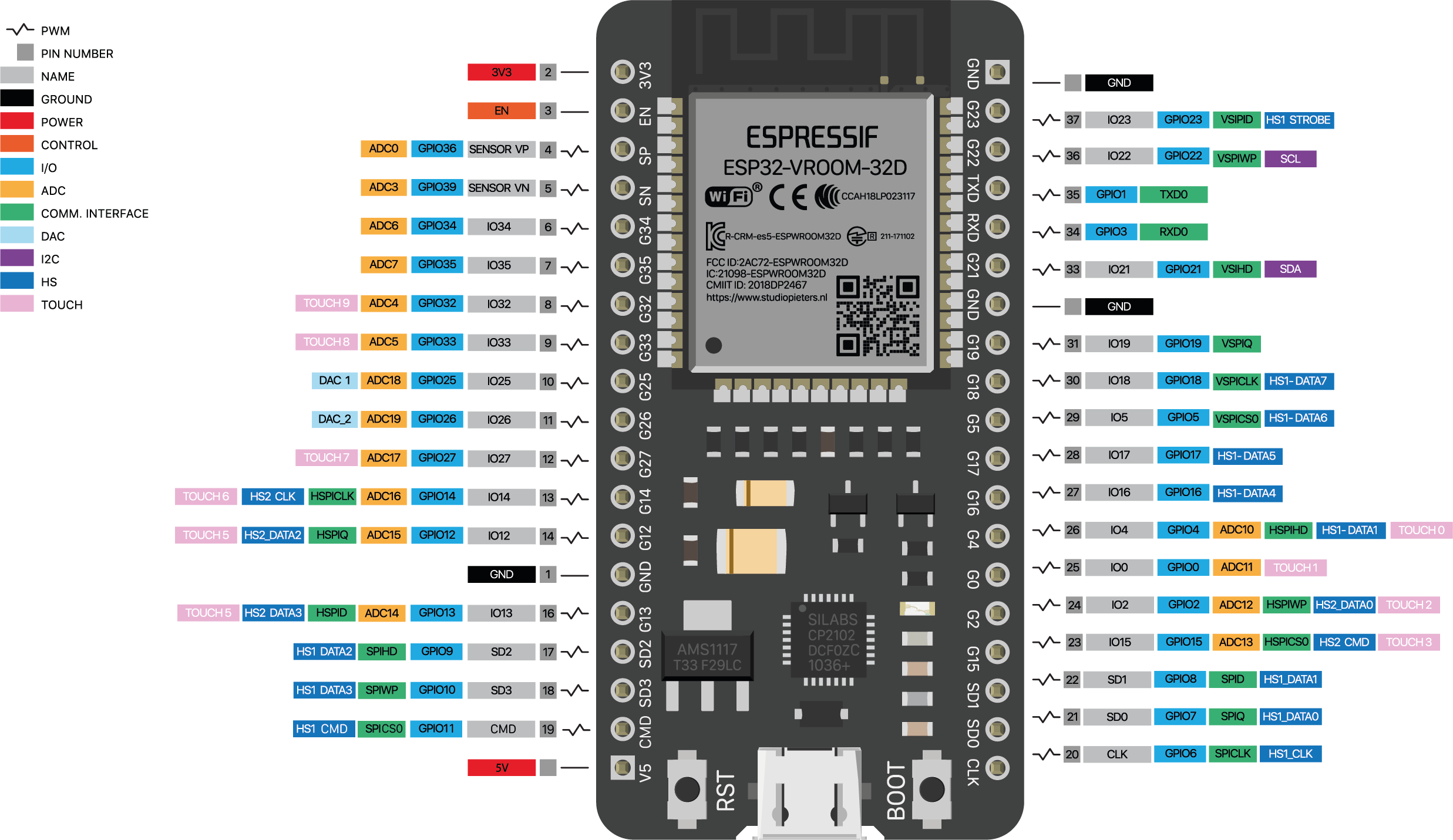

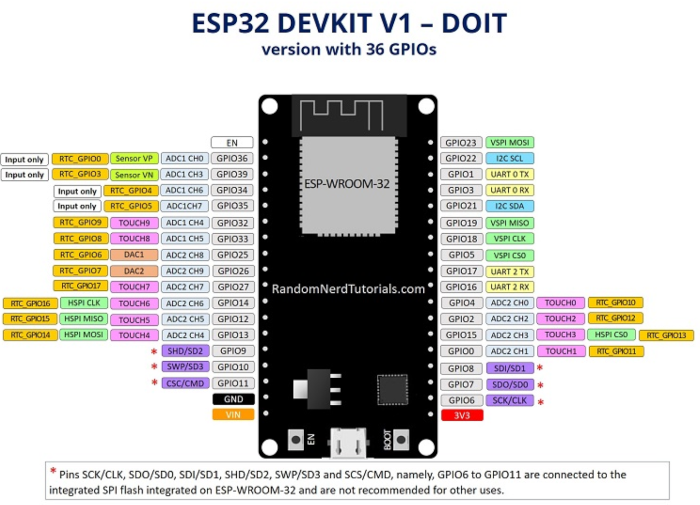

=Pinout for ESP32= | =Pinout for ESP32= | ||

This is the pinout for my ESP32 | This is the pinout for one of my ESP32<br> | ||

[[File:ESP32-38 PIN-DEVBOARD.png| | [[File:ESP32-38 PIN-DEVBOARD.png|600px]] | ||

This is the pinout for another one be careful<br> | |||

[[File:Esp32 devkit v1 doit.png|600px]] | |||

=UDEV= | =UDEV= | ||

| Line 304: | Line 318: | ||

To monitor you can do the following. This can be exited using the ctrl + ] (like telnet | To monitor you can do the following. This can be exited using the ctrl + ] (like telnet | ||

<syntaxhighlight lang="bash"> | <syntaxhighlight lang="bash"> | ||

idf.py -p /dev/ttyUSB0 flash | idf.py -p /dev/ttyUSB0 monitor | ||

</syntaxhighlight> | |||

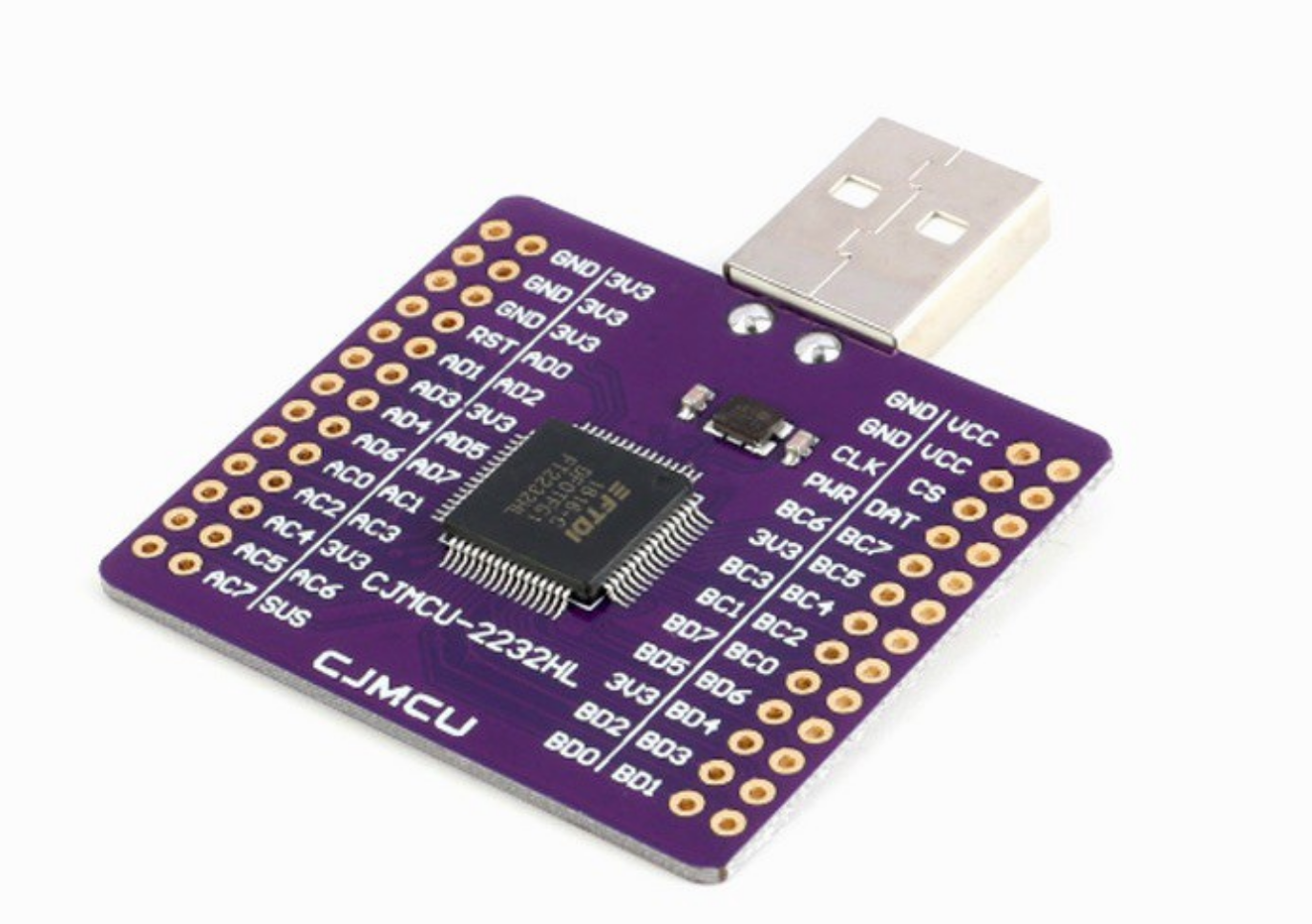

==Second Attempt CJMCU-2232 FT2232HL== | |||

I eventually gave up trying to get the FT232R to work. I believe it is because there in no chip to handle the JTAG and the UART at the same time this let me to look at alternatives | |||

<br> | |||

Plugged two these in but both blew up when connected.<br> | |||

[[File:FT2232HL.png|300px]]<br> | |||

I used the connections provided on by [https://medium.com/@manuel.bl/low-cost-esp32-in-circuit-debugging-dbbee39e508b here] | |||

*GPIO12 — AD1 (TDI) | |||

*GPIO15 — AD2 (TDO) | |||

*GPIO13 — AD0 (TCK) | |||

*GPIO14 — AD3 (TMS) | |||

*GND — GND | |||

I did not plug in the VCC and still do not understand why this happened. | |||

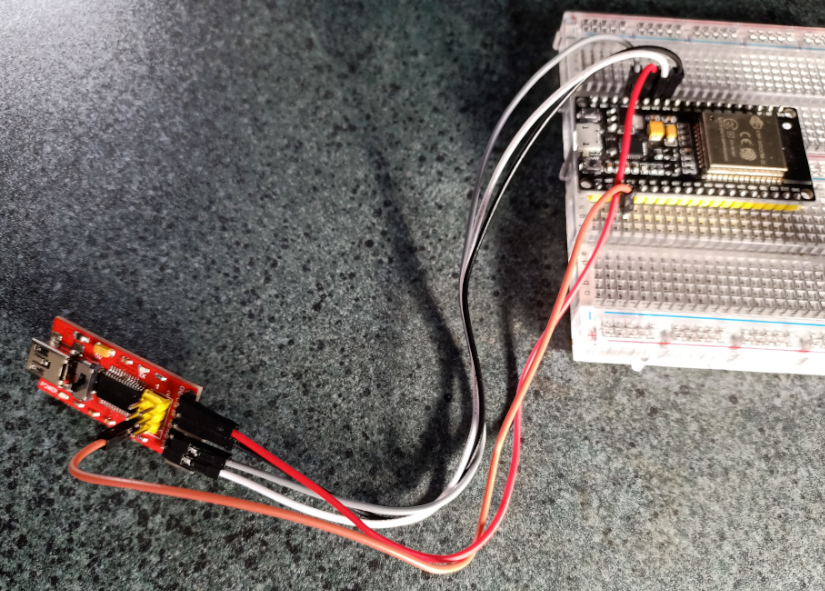

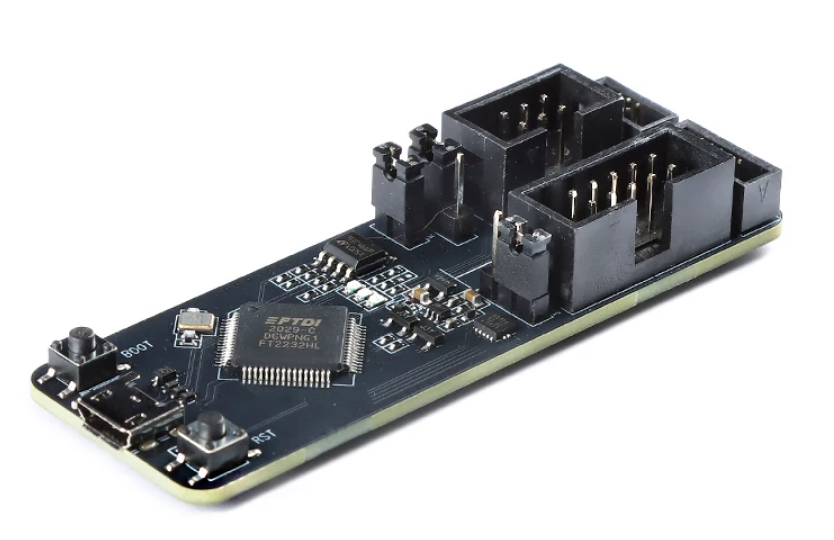

==Third Attempt ESP-PROG== | |||

I now am trying and seen it work the standard way to approach this using the esp-prog. These are relatively cheap to buy ~$30 and can be bought online but no where in NZ<br> | |||

[[File:ESP Prog.png| 300px]]<br> | |||

===Current Wiring=== | |||

*GPIO12 — AD1 (TDI) Purple | |||

*GPIO15 — AD2 (TDO) Blue | |||

*GPIO13 — AD0 (TCK) Grey | |||

*GPIO14 — AD3 (TMS) White | |||

*GND — (GND) Green | |||

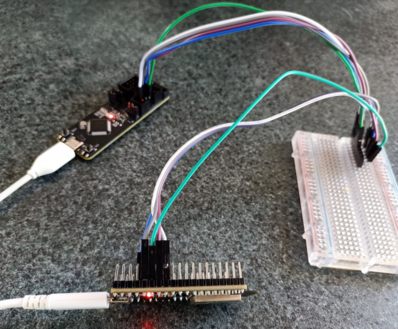

An here it is all wired up. Feel I have learnt a bit along the way<br> | |||

[[File:Esp32 esprog 30.png|300px]]<br> | |||

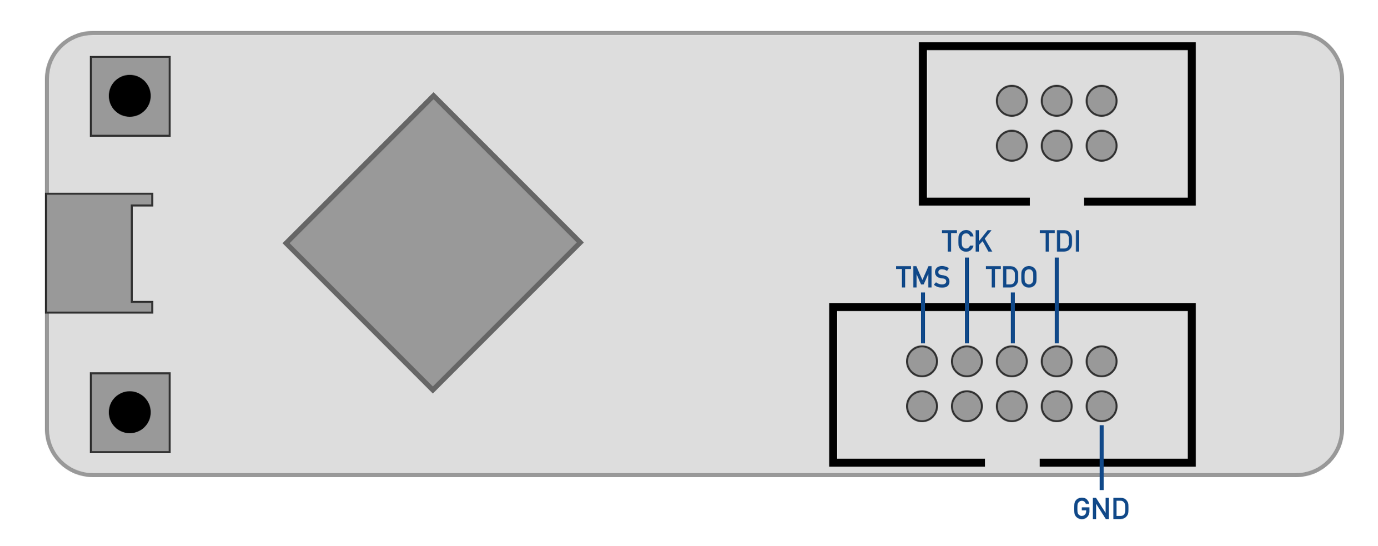

To wire this up we use the following<br> | |||

[[File:Esp-prog-wiring.png|300px]]<br> | |||

I put the gnd in the middle row of as the end pin is power on one side. Having blown up the previous attempts I wanted to be doubly sure.<br> | |||

===Udev Rules=== | |||

Revisiting this I could not get to work because of udev rules | |||

<syntaxhighlight lang="bash"> | |||

Info : Listening on port 6666 for tcl connections | |||

Info : Listening on port 4444 for telnet connections | |||

Error: libusb_open() failed with LIBUSB_ERROR_ACCESS | |||

Error: no device found | |||

Error: unable to open ftdi device with vid 0403, pid 6010, description '*', serial '*' at bus location '*' | |||

Error: no device found | |||

Error: unable to open ftdi device with vid 0403, pid 6014, description '*', serial '*' at bus location '*' | |||

</syntaxhighlight> | |||

Adding the following worked for me | |||

<syntaxhighlight lang="bash"> | |||

ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", MODE="0666", ENV{ID_MM_DEVICE_IGNORE}="1" | |||

ATTRS{idVendor}=="10c4", ATTRS{idProduct}=="ea60", MODE="0666", ENV{ID_MM_DEVICE_IGNORE}="1" | |||

</syntaxhighlight> | |||

===Override Bootstrap pin=== | |||

When the ESP32 is connected to the ESP-PROG the flash does not work. This is because the GPIO12 is which is a bootstrap pin that controls VDD_SDIO. To override this we can use the following | |||

<syntaxhighlight lang="bash"> | |||

python `which espefuse.py` --port /dev/ttyUSB2 set_flash_voltage 3.3V | |||

</syntaxhighlight> | |||

===Starting Debugger=== | |||

The debugger is a separate process and runs independently from the debugging screen. For the openocd we do the following to start it. | |||

<syntaxhighlight lang="bash"> | |||

. ~/esp/esp-idf/export.sh | |||

cd ~/.espressif/tools/openocd-esp32/v0.11.0-esp32-20220706/openocd-esp32 | |||

bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg | |||

Open On-Chip Debugger v0.11.0-esp32-20220706 (2022-07-06-15:48) | |||

Licensed under GNU GPL v2 | |||

For bug reports, read | |||

http://openocd.org/doc/doxygen/bugs.html | |||

adapter speed: 20000 kHz | |||

WARNING: boards/esp-wroom-32.cfg is deprecated, and may be removed in a future release. | |||

Info : Listening on port 6666 for tcl connections | |||

Info : Listening on port 4444 for telnet connections | |||

Info : ftdi: if you experience problems at higher adapter clocks, try the command "ftdi tdo_sample_edge falling" | |||

Info : clock speed 20000 kHz | |||

Info : JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1) | |||

Info : JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1) | |||

Info : [esp32.cpu0] Debug controller was reset. | |||

Info : [esp32.cpu0] Core was reset. | |||

Error: Unexpected OCD_ID = 00000000 | |||

Error: Unexpected OCD_ID = 00000000 | |||

Error: Unexpected OCD_ID = 00000000 | |||

Warn : target esp32.cpu1 examination failed | |||

Error: Unexpected OCD_ID = 00000000 | |||

Error: Unexpected OCD_ID = 00000000 | |||

Error: Unexpected OCD_ID = 00000000 | |||

Info : starting gdb server for esp32.cpu0 on 3333 | |||

Info : Listening on port 3333 for gdb connections | |||

... | |||

</syntaxhighlight> | |||

===Starting Debugging session=== | |||

For the debugging we do need to do the following. Set up the environment and get to your project directory | |||

<syntaxhighlight lang="bash"> | |||

. ./esp/esp-idf/export.sh | |||

cd ~/dev/projects/ESP/hello_world | |||

</syntaxhighlight> | |||

Make a gdbinit file | |||

<syntaxhighlight lang="text"> | |||

set remotetimeout 100 | |||

target remote :3333 | |||

mon reset halt | |||

thb app_main | |||

x $a1=0 | |||

c | |||

</syntaxhighlight> | |||

Start debugging | |||

<syntaxhighlight lang="bash"> | |||

xtensa-esp32-elf-gdb -x gdbinit build/hello-world.elf | |||

</syntaxhighlight> | |||

When loaded we can add a breakpoint at line 30 and continue | |||

<syntaxhighlight lang="bash"> | |||

[Switching to Thread 1073438564] | |||

Thread 1 hit Temporary breakpoint 1, app_main () at ../main/hello_world_main.c:20 | |||

20 { | |||

(gdb) b 37 | |||

Breakpoint 2 at 0x400d43a2: file ../main/hello_world_main.c, line 37. | |||

(gdb) c | |||

Continuing. | |||

Note: automatically using hardware breakpoints for read-only addresses. | |||

esp32.cpu0: Target halted, PC=0x400D43A2, debug_reason=00000001 | |||

Set GDB target to 'esp32.cpu0' | |||

esp32.cpu1: Target halted, PC=0x400E345A, debug_reason=00000000 | |||

Thread 1 hit Breakpoint 2, app_main () at ../main/hello_world_main.c:37 | |||

37 printf("test 1 %d, ", a); | |||

(gdb) p a | |||

$1 = 10 | |||

</syntaxhighlight> | </syntaxhighlight> | ||

==VS Code== | ==VS Code== | ||

===Bug with VS Code=== | ===Bug with VS Code=== | ||

| Line 334: | Line 471: | ||

======================================================= | ======================================================= | ||

... | ... | ||

</syntaxhighlight> | |||

==Products== | |||

*Arduino Compatible Dual Ultrasonic Sensor Module https://www.jaycar.co.nz/medias/sys_master/images/images/9677390118942/XC4442-manualMain.pdf | |||

*Logic Level Convertor https://www.jaycar.co.nz/medias/sys_master/images/images/9677413122078/XC4486-dataSheetMain.pdf | |||

*Rasp PI Camera https://www.jaycar.co.nz/medias/sys_master/images/images/9677446971422/XC9020-manualMain.pdf | |||

=Rust on ESP32C3= | |||

This is my first foray into ESP32c3. | |||

==Environment== | |||

I had to set up rust which I followed the usually help and used the following commands | |||

<syntaxhighlight lang="bash"> | |||

cargo install espup | |||

espup install | |||

rustup toolchain list | |||

cargo install cargo-generate | |||

</syntaxhighlight> | |||

==Blink== | |||

So rust is split into std and no_std. Basically you get the standard function with one of them, I wont say which. We are going to working with no_std because I can. With this we can generate a hello world to get up going. | |||

<syntaxhighlight lang="bash"> | |||

cargo generate esp-rs/esp-template | |||

</syntaxhighlight> | |||

This prompt with lots of questions but at the end you get a folder and you can run | |||

<syntaxhighlight lang="bash"> | |||

cargo run | |||

</syntaxhighlight> | |||

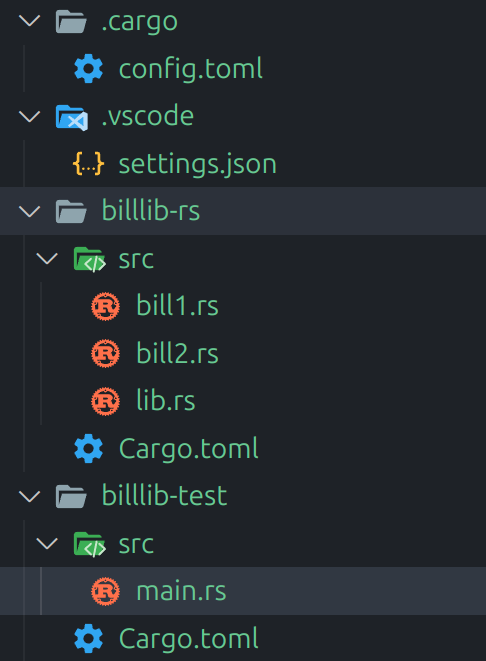

==Library== | |||

So first off wanted a library for my gc9A01 so had to relearn rust again to get going so here is how you do it briefly<br> | |||

[[File:Rust lib structure.png]]<br> | |||

We put the lib functions is bill1.rs and bill2.rs and function exported in lib.rs. | |||

Here is lib.rs | |||

<syntaxhighlight lang="rs"> | |||

#![cfg_attr(not(test), no_std)] | |||

pub mod bill1; | |||

pub mod bill2; | |||

</syntaxhighlight> | |||

Here is bill1.rs | |||

<syntaxhighlight lang="rs"> | |||

use esp_println::println; | |||

pub fn test_function1() { | |||

println!("test_function 1"); | |||

} | |||

</syntaxhighlight> | |||

And we can now use this in bill-test, main.rs | |||

<syntaxhighlight lang="rs" highlight="10,38"> | |||

#![no_std] | |||

#![no_main] | |||

extern crate alloc; | |||

use core::mem::MaybeUninit; | |||

use esp_backtrace as _; | |||

use esp_println::println; | |||

use hal::{clock::ClockControl, peripherals::Peripherals, prelude::*, Delay}; | |||

use billlib::bill1; | |||

#[global_allocator] | |||

static ALLOCATOR: esp_alloc::EspHeap = esp_alloc::EspHeap::empty(); | |||

fn init_heap() { | |||

const HEAP_SIZE: usize = 32 * 1024; | |||

static mut HEAP: MaybeUninit<[u8; HEAP_SIZE]> = MaybeUninit::uninit(); | |||

unsafe { | |||

ALLOCATOR.init(HEAP.as_mut_ptr() as *mut u8, HEAP_SIZE); | |||

} | |||

} | |||

#[entry] | |||

fn main() -> ! { | |||

init_heap(); | |||

let peripherals = Peripherals::take(); | |||

let system = peripherals.SYSTEM.split(); | |||

let clocks = ClockControl::max(system.clock_control).freeze(); | |||

let mut delay = Delay::new(&clocks); | |||

// setup logger | |||

// To change the log_level change the env section in .cargo/config.toml | |||

// or remove it and set ESP_LOGLEVEL manually before running cargo run | |||

// this requires a clean rebuild because of https://github.com/rust-lang/cargo/issues/10358 | |||

esp_println::logger::init_logger_from_env(); | |||

log::info!("Logger is setup"); | |||

bill1::test_function1(); | |||

// println!("Hello world!"); | |||

loop { | |||

println!("Loop..."); | |||

delay.delay_ms(500u32); | |||

} | |||

} | |||

</syntaxhighlight> | |||

==Debugging Again== | |||

Got my esp-prog out and managed get it going again but another hour lost. The basics seem to work. Here is the command, the same as above | |||

<syntaxhighlight lang="sh"> | |||

. ~/esp/esp-idf/export.sh | |||

cd ~/.espressif/tools/openocd-esp32/v0.12.0-esp32-20230921/openocd-esp32/ | |||

bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg | |||

</syntaxhighlight> | |||

When running openocd this is a working output. | |||

<syntaxhighlight lang="txt"> | |||

iwiseman@oliver:~/.espressif/tools/openocd-esp32/v0.12.0-esp32-20230921/openocd-esp32$ bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg | |||

Open On-Chip Debugger v0.12.0-esp32-20230921 (2023-09-21-13:41) | |||

Licensed under GNU GPL v2 | |||

For bug reports, read | |||

http://openocd.org/doc/doxygen/bugs.html | |||

adapter speed: 20000 kHz | |||

WARNING: boards/esp-wroom-32.cfg is deprecated, and may be removed in a future release. | |||

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'. | |||

Info : Listening on port 6666 for tcl connections | |||

Info : Listening on port 4444 for telnet connections | |||

Info : ftdi: if you experience problems at higher adapter clocks, try the command "ftdi tdo_sample_edge falling" | |||

Info : clock speed 20000 kHz | |||

Info : JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1) | |||

Info : JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1) | |||

Info : starting gdb server for esp32.cpu0 on 3333 | |||

Info : Listening on port 3333 for gdb connections | |||

Info : [esp32.cpu0] Target halted, PC=0x400D5547, debug_reason=00000001 | |||

Info : [esp32.cpu0] Reset cause (3) - (Software core reset) | |||

Info : Set GDB target to 'esp32.cpu0' | |||

Info : [esp32.cpu1] Target halted, PC=0x4008466A, debug_reason=00000000 | |||

Info : [esp32.cpu1] Reset cause (14) - (CPU1 reset by CPU0) | |||

</syntaxhighlight> | |||

For vscode I copied the examples using ctrl-p Show Example Projects and copied the hello world. The produced a launch.json | |||

<syntaxhighlight lang="json"> | |||

{ | |||

"version": "0.2.0", | |||

"configurations": [ | |||

{ | |||

"type": "espidf", | |||

"name": "Launch", | |||

"request": "launch" | |||

} | |||

] | |||

} | |||

</syntaxhighlight> | </syntaxhighlight> | ||

Latest revision as of 04:08, 1 May 2025

Introduction

As the little grey cells get older probably time to give to pointers to myself

Arduino

Installation on ubuntu is

sudo snap install arduino

The important step is to address for the board configuration

https://dl.espressif.com/dl/package_esp32_index.json

This can be install by following steps on https://randomnerdtutorials.com/installing-the-esp32-board-in-arduino-ide-windows-instructions/

UDev Rules

Here is what I use for my WROOM 32d in /etc/udev/rules.d/98-esp32.rules

ATTRS{idVendor}=="10c4", ATTRS{idProduct}=="ea60", MODE="0666", ENV{ID_MM_DEVICE_IGNORE}="1"I also add myself to the dailout group with

sudo usermod -a -G dialout $USER

Building openocd

This is a cop out as I should fix the errors and feed back but here we go.

Ignore maybe-uninitialized

#pragma GCC diagnostic push

#pragma GCC diagnostic ignored "-Wmaybe-uninitialized"

Pinout for ESP32

This is the pinout for one of my ESP32

This is the pinout for another one be careful

This is the pinout for another one be careful

UDEV

To make sure the device is recogised we need to add rules to /etc/udev/rules.d/

This is my board and my UART interface. The plugdev is the important bit as we need to not run things as root for some strange reason.

ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6001", MODE="660", GROUP="plugdev", TAG+="uaccess"

ATTRS{idVendor}=="10c4", ATTRS{idProduct}=="ea60", MODE="660", GROUP="plugdev", TAG+="uaccess"openocd and FT232R

Openocd User Manual

This can be found [here]

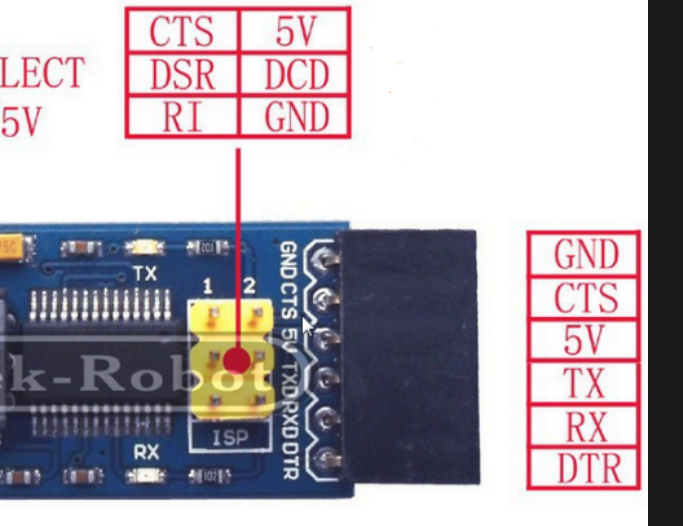

FT232

This is what I believe my FT232 is [here]

The connector shown for a similar board gives

Connecting

The following was suggested to get the JTAG interface to work.

GPIO15=TDO

GPIO12=TDI

GPIO13=TCK

GPIO14=TMS

GND=GND

ft232r.cfg

This is what I have used for ft232.cfg

interface ft232r

adapter_khz 3000

ft232r_tck_num TXD

ft232r_tdi_num RXD

ft232r_tdo_num RI

ft232r_tms_num CTS

ft232r_trst_num DTR

ft232r_srst_num DCDRunning Open OCD Debugger

OCD Side

The scripts are written in TCL. Here is the command to run

cd ~/.espressif/tools/openocd-esp32/v0.10.0-esp32-20210401/openocd-esp32/bin

./openocd -d3 -f ../share/openocd/scripts/interface/ft232r.cfg -f ../share/openocd/scripts/board/esp-wroom-32.cfg

GDB Side

The gdbinit file

set remotetimeout 100

target remote :3333

mon reset halt

thb app_main

x $a1=0

cAnd here is the build and execute

cp -r \$IDF_PATH/examples/get-started/blink .

cd blink/

cd build

esptool.py --chip esp32 -p /dev/ttyUSB0 -b 460800 --before=default_reset --after=hard_reset write_flash --flash_mode dio --flash_freq 40m --flash_size 2MB 0x8000 partition_table/partition-table.bin 0x1000 bootloader/bootloader.bin 0x10000 blink.bin

cd -

xtensa-esp32-elf-gdb -x gdbinit build/blink.elf

Distilled Script

I have worked through the scripts provided with openocd and this is the script I believe is run from the above command.

interface ft232r

#ft232r_restore_serial 0x15

ft232r_tdi_num TXD

ft232r_tck_num DTR

ft232r_tdo_num RXD

ft232r_tms_num CTS

# trst/srst are not used but must have different values than above

ft232r_trst_num DCD

ft232r_srst_num RI

#reset_config none

adapter_khz 500

set ESP32_FLASH_VOLTAGE 3.3

# ESP_COMMON.CFG

set _FLASH_SIZE "auto"

puts "==== FLASH_SIZE $_FLASH_SIZE"

set _SEMIHOST_BASEDIR "."

puts "==== SEMIHOST_BASEDIR $_SEMIHOST_BASEDIR"

###

### configure_esp_workarea

###

proc configure_esp_workarea { TGT CODE_ADDR CODE_SZ DATA_ADDR DATA_SZ } {

#WARNING: be careful when selecting working ares for code and data, they should not overlap due to ESP32 physical memory mappings

$TGT configure -work-area-phys $CODE_ADDR -work-area-virt $CODE_ADDR -work-area-size $CODE_SZ -work-area-backup 1

# since ESP32 cannot use single address space for code and data we need additional working area to keep data

$TGT configure -alt-work-area-phys $DATA_ADDR -alt-work-area-virt $DATA_ADDR -alt-work-area-size $DATA_SZ -alt-work-area-backup 1

}

###

### configure_esp_workarea

###

proc configure_esp_flash_bank { TGT DRV SIZE } {

set _SIZE SIZE

# special value for flash driver

set _SIZE 0

# whole flash for programming purposes

# TODO: remove it when support for GDB's 'load' comand is implemented

flash bank $TGT.flash $DRV 0x0 $_SIZE 0 0 $TGT

# So define mapped flash regions as separate flashes

# OOCD creates memory map using registered flash banks

flash bank $TGT.irom $DRV 0x0 0 0 0 $TGT

flash bank $TGT.drom $DRV 0x0 0 0 0 $TGT

}

# ESP32.cfg

# The ESP32 only supports JTAG.

# transport select jtag

# Target specific registers

set EFUSE_BLK0_RDATA1_REG 0x3ff5A004

set _CHIPNAME esp32

puts "==== CHIPNAME $_CHIPNAME"

set _CPUTAPID 0x120034e5

puts "==== CPUTAPID $_CPUTAPID"

set _ONLYCPU 3

puts "==== ONLYCPU $_ONLYCPU"

set _FLASH_VOLTAGE $ESP32_FLASH_VOLTAGE

puts "==== FLASH_VOLTAGE $_FLASH_VOLTAGE"

set _CPU0NAME cpu0

set _CPU1NAME cpu1

set _TARGETNAME_0 $_CHIPNAME.$_CPU0NAME

set _TARGETNAME_1 $_CHIPNAME.$_CPU1NAME

set _RTOS "FreeRTOS"

puts "==== RTOS $_RTOS"

jtag newtap $_CHIPNAME $_CPU0NAME -irlen 5 -expected-id $_CPUTAPID

jtag newtap $_CHIPNAME $_CPU1NAME -irlen 5 -expected-id $_CPUTAPID

target create $_TARGETNAME_0 $_CHIPNAME -endian little -chain-position $_TARGETNAME_0 -coreid 0 -rtos $_RTOS

configure_esp_workarea $_TARGETNAME_0 0x40090000 0x3400 0x3FFC0000 0x10000

configure_esp_flash_bank $_TARGETNAME_0 $_CHIPNAME $_FLASH_SIZE

# APP-CPU

target create $_TARGETNAME_1 $_CHIPNAME -endian little -chain-position $_TARGETNAME_1 -coreid 1 -rtos $_RTOS

configure_esp_flash_bank $_TARGETNAME_1 $_CHIPNAME $_FLASH_SIZE

target smp $_TARGETNAME_0 $_TARGETNAME_1

$_TARGETNAME_0 esp32 flashbootstrap $_FLASH_VOLTAGE

$_TARGETNAME_0 xtensa maskisr on

$_TARGETNAME_0 xtensa smpbreak BreakIn BreakOut

$_TARGETNAME_0 esp semihost_basedir $_SEMIHOST_BASEDIR

$_TARGETNAME_1 configure -event gdb-attach {

$_TARGETNAME_1 xtensa smpbreak BreakIn BreakOut

# necessary to auto-probe flash bank when GDB is connected

halt

}

puts "==================================== Scooby doo 1"

Debug Progress

I have logged the bug https://github.com/espressif/openocd-esp32/issues/157 which is still open. For comparison here is the log which I am told contains no errors however it hangs on the GDB side.

iwiseman@oliver:~/dev/openocd-esp32$ grep -v ^Debug ~/iain_500.log

Open On-Chip Debugger v0.10.0-esp32-20210401 (2021-04-01-15:45)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

User : 13 1 options.c:57 configuration_output_handler(): debug_level: 3

User : 14 1 options.c:57 configuration_output_handler():

Info : 36 1 transport.c:117 allow_transports(): only one transport option; autoselect 'jtag'

User : 81 2 options.c:57 configuration_output_handler(): adapter speed: 500 kHz

User : 82 2 options.c:57 configuration_output_handler():

User : 86 2 command.c:770 jim_echo(): WARNING: boards/esp-wroom-32.cfg is deprecated, and may be removed in a future release.

Warn : 89 2 transport.c:297 jim_transport_select(): Transport "jtag" was already selected

$_TARGETNAME_0 xtensa smpbreak BreakIn BreakOut

# necessary to auto-probe flash bank when GDB is connected

halt

$_TARGETNAME_1 xtensa smpbreak BreakIn BreakOut

# necessary to auto-probe flash bank when GDB is connected

halt

Info : 420 4 server.c:311 add_service(): Listening on port 6666 for tcl connections

Info : 421 4 server.c:311 add_service(): Listening on port 4444 for telnet connections

Info : 504 20 core.c:1449 adapter_init(): clock speed 500 kHz

Info : 518 28 core.c:1027 jtag_examine_chain_display(): JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : 519 28 core.c:1027 jtag_examine_chain_display(): JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : 560 1820 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x4000941D, debug_reason=00000000

Info : 570 3601 xtensa.c:1859 xtensa_poll(): esp32.cpu1: Target halted, PC=0x400076DD, debug_reason=00000000

Info : 643 3953 server.c:311 add_service(): Listening on port 3333 for gdb connections

Info : 644 4181 server.c:100 add_connection(): accepting 'gdb' connection on tcp/3333

Warn : 650 4181 FreeRTOS.c:702 FreeRTOS_update_threads(): No symbols for FreeRTOS!

$_TARGETNAME_0 xtensa smpbreak BreakIn BreakOut

# necessary to auto-probe flash bank when GDB is connected

halt

Info : 772 31204 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x40091C2A, debug_reason=00000001

Info : 774 31212 esp_xtensa_smp.c:234 esp_xtensa_smp_update_halt_gdb(): Set GDB target to 'esp32.cpu0'

Info : 948 45312 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 0: 0x10020 -> 0x3f400020, 23 KB

Info : 949 45312 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 1: 0x20020 -> 0x400d0020, 75 KB

Info : 1043 71826 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x40091C2A, debug_reason=00000001

Info : 1177 85248 esp_xtensa.c:883 esp_xtensa_probe(): Auto-detected flash bank 'esp32.cpu0.flash' size 4096 KB

Info : 1178 85248 esp_xtensa.c:885 esp_xtensa_probe(): Using flash bank 'esp32.cpu0.flash' size 4096 KB

Info : 1282 112259 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x40091C2A, debug_reason=00000001

Info : 1455 126342 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 0: 0x10020 -> 0x3f400020, 23 KB

Info : 1456 126342 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 1: 0x20020 -> 0x400d0020, 75 KB

Info : 1457 126342 esp_xtensa.c:885 esp_xtensa_probe(): Using flash bank 'esp32.cpu0.irom' size 76 KB

Info : 1561 153325 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x40091C2A, debug_reason=00000001

Info : 1734 167393 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 0: 0x10020 -> 0x3f400020, 23 KB

Info : 1735 167393 esp_xtensa.c:368 esp_xtensa_get_mappings(): Flash mapping 1: 0x20020 -> 0x400d0020, 75 KB

Info : 1736 167393 esp_xtensa.c:885 esp_xtensa_probe(): Using flash bank 'esp32.cpu0.drom' size 24 KB

Info : 1738 167393 gdb_server.c:1011 gdb_new_connection(): New GDB Connection: 1, Target esp32.cpu0, state: halted

Warn : 1742 167393 gdb_server.c:441 gdb_put_packet_inner(): negative reply, retrying

<threads>

</threads>

#02'

<threads>

</threads>

#02'

<memory type="flash" start="0x00000000" length="0x400000">

<property name="blocksize">0x1000</property>

</memory>

<memory type="ram" start="0x00400000" length="0x3f000000"/>

<memory type="flash" start="0x3f400000" length="0x6000">

<property name="blocksize">0x1000</property>

</memory>

<memory type="ram" start="0x3f406000" length="0xcca000"/>

<memory type="flash" start="0x400d0000" length="0x13000">

<property name="blocksize">0x1000</property>

</memory>

<memory type="ram" start="0x400e3000" length="0xbff1d000"/>

</memory-map>

#23'

Info : 1839 167653 core.c:1027 jtag_examine_chain_display(): JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : 1841 167653 core.c:1027 jtag_examine_chain_display(): JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : 1901 168534 xtensa.c:1797 xtensa_poll(): esp32.cpu0: Debug controller was reset.

Info : 1904 168545 xtensa.c:1803 xtensa_poll(): esp32.cpu0: Core was reset.

Info : 1912 170303 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x500000CF, debug_reason=00000000

Info : 1995 170854 xtensa.c:1803 xtensa_poll(): esp32.cpu0: Core was reset.

Info : 2003 172610 xtensa.c:1859 xtensa_poll(): esp32.cpu0: Target halted, PC=0x40000400, debug_reason=00000000

Info : 2010 172623 xtensa.c:1797 xtensa_poll(): esp32.cpu1: Debug controller was reset.

Info : 2013 172633 xtensa.c:1803 xtensa_poll(): esp32.cpu1: Core was reset.

Info : 2021 174376 xtensa.c:1859 xtensa_poll(): esp32.cpu1: Target halted, PC=0x40000400, debug_reason=00000000Getting Started IDF

Uploading

With my ESP32 you have to hold the boot and reset to do an upload

idf.py -p /dev/ttyUSB0 flash

Monitoring

To monitor you can do the following. This can be exited using the ctrl + ] (like telnet

idf.py -p /dev/ttyUSB0 monitor

Second Attempt CJMCU-2232 FT2232HL

I eventually gave up trying to get the FT232R to work. I believe it is because there in no chip to handle the JTAG and the UART at the same time this let me to look at alternatives

Plugged two these in but both blew up when connected.

I used the connections provided on by here

- GPIO12 — AD1 (TDI)

- GPIO15 — AD2 (TDO)

- GPIO13 — AD0 (TCK)

- GPIO14 — AD3 (TMS)

- GND — GND

I did not plug in the VCC and still do not understand why this happened.

Third Attempt ESP-PROG

I now am trying and seen it work the standard way to approach this using the esp-prog. These are relatively cheap to buy ~$30 and can be bought online but no where in NZ

Current Wiring

- GPIO12 — AD1 (TDI) Purple

- GPIO15 — AD2 (TDO) Blue

- GPIO13 — AD0 (TCK) Grey

- GPIO14 — AD3 (TMS) White

- GND — (GND) Green

An here it is all wired up. Feel I have learnt a bit along the way

To wire this up we use the following

I put the gnd in the middle row of as the end pin is power on one side. Having blown up the previous attempts I wanted to be doubly sure.

Udev Rules

Revisiting this I could not get to work because of udev rules

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Error: libusb_open() failed with LIBUSB_ERROR_ACCESS

Error: no device found

Error: unable to open ftdi device with vid 0403, pid 6010, description '*', serial '*' at bus location '*'

Error: no device found

Error: unable to open ftdi device with vid 0403, pid 6014, description '*', serial '*' at bus location '*'

Adding the following worked for me

ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", MODE="0666", ENV{ID_MM_DEVICE_IGNORE}="1"

ATTRS{idVendor}=="10c4", ATTRS{idProduct}=="ea60", MODE="0666", ENV{ID_MM_DEVICE_IGNORE}="1"

Override Bootstrap pin

When the ESP32 is connected to the ESP-PROG the flash does not work. This is because the GPIO12 is which is a bootstrap pin that controls VDD_SDIO. To override this we can use the following

python `which espefuse.py` --port /dev/ttyUSB2 set_flash_voltage 3.3V

Starting Debugger

The debugger is a separate process and runs independently from the debugging screen. For the openocd we do the following to start it.

. ~/esp/esp-idf/export.sh

cd ~/.espressif/tools/openocd-esp32/v0.11.0-esp32-20220706/openocd-esp32

bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg

Open On-Chip Debugger v0.11.0-esp32-20220706 (2022-07-06-15:48)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

adapter speed: 20000 kHz

WARNING: boards/esp-wroom-32.cfg is deprecated, and may be removed in a future release.

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : ftdi: if you experience problems at higher adapter clocks, try the command "ftdi tdo_sample_edge falling"

Info : clock speed 20000 kHz

Info : JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : [esp32.cpu0] Debug controller was reset.

Info : [esp32.cpu0] Core was reset.

Error: Unexpected OCD_ID = 00000000

Error: Unexpected OCD_ID = 00000000

Error: Unexpected OCD_ID = 00000000

Warn : target esp32.cpu1 examination failed

Error: Unexpected OCD_ID = 00000000

Error: Unexpected OCD_ID = 00000000

Error: Unexpected OCD_ID = 00000000

Info : starting gdb server for esp32.cpu0 on 3333

Info : Listening on port 3333 for gdb connections

...

Starting Debugging session

For the debugging we do need to do the following. Set up the environment and get to your project directory

. ./esp/esp-idf/export.sh

cd ~/dev/projects/ESP/hello_world

Make a gdbinit file

set remotetimeout 100

target remote :3333

mon reset halt

thb app_main

x $a1=0

c

Start debugging

xtensa-esp32-elf-gdb -x gdbinit build/hello-world.elf

When loaded we can add a breakpoint at line 30 and continue

[Switching to Thread 1073438564]

Thread 1 hit Temporary breakpoint 1, app_main () at ../main/hello_world_main.c:20

20 {

(gdb) b 37

Breakpoint 2 at 0x400d43a2: file ../main/hello_world_main.c, line 37.

(gdb) c

Continuing.

Note: automatically using hardware breakpoints for read-only addresses.

esp32.cpu0: Target halted, PC=0x400D43A2, debug_reason=00000001

Set GDB target to 'esp32.cpu0'

esp32.cpu1: Target halted, PC=0x400E345A, debug_reason=00000000

Thread 1 hit Breakpoint 2, app_main () at ../main/hello_world_main.c:37

37 printf("test 1 %d, ", a);

(gdb) p a

$1 = 10

VS Code

Bug with VS Code

There is an expired cert in the build system. When build with VS Code extension this shows

Generating x509_crt_bundle

FAILED: esp-idf/mbedtls/x509_crt_bundle

cmd.exe /C "cd /D C:\Users\yahsa\Desktop\NTU\FYP\ESP_Workspace\blink\build\esp-idf\mbedtls && C:\Users\yahsa\esp.espressif\python_env\idf4.3_py3.8_env\Scripts\python.exe C:/Users/yahsa/esp/esp-idf/components/mbedtls/esp_crt_bundle/gen_crt_bundle.py --input C:/Users/yahsa/esp/esp-idf/components/mbedtls/esp_crt_bundle/cacrt_all.pem -q"

gen_crt_bundle.py: Invalid certificate in C:/Users/yahsa/esp/esp-idf/components/mbedtls/esp_crt_bundle/cacrt_all.pem

Invalid certificate

ninja: build stopped: subcommand failed.

The current fix was to remove the ECC-ACC from ./esp-idf/components/mbedtls/esp_crt_bundle/cacrt_all.pem

...

EC-ACC

======

-----BEGIN CERTIFICATE-----

MIIFVjCCBD6gAwIBAgIQ7is969Qh3hSoYqwE893EATANBgkqhkiG9w0BAQUFADCB8zELMAkGA1UE

BhMCRVMxOzA5BgNVBAoTMkFnZW5jaWEgQ2F0YWxhbmEgZGUgQ2VydGlmaWNhY2lvIChOSUYgUS0w

...

E/rKS03Z7lNGBjvGTq2TWoF+bCpLagVFjPIhpDGQh2xlnJ2lYJU6Un/10asIbvPuW/mIPX64b24D

5EI=

-----END CERTIFICATE-----

Hellenic Academic and Research Institutions RootCA 2011

=======================================================

...

Products

- Arduino Compatible Dual Ultrasonic Sensor Module https://www.jaycar.co.nz/medias/sys_master/images/images/9677390118942/XC4442-manualMain.pdf

- Logic Level Convertor https://www.jaycar.co.nz/medias/sys_master/images/images/9677413122078/XC4486-dataSheetMain.pdf

- Rasp PI Camera https://www.jaycar.co.nz/medias/sys_master/images/images/9677446971422/XC9020-manualMain.pdf

Rust on ESP32C3

This is my first foray into ESP32c3.

Environment

I had to set up rust which I followed the usually help and used the following commands

cargo install espup

espup install

rustup toolchain list

cargo install cargo-generate

Blink

So rust is split into std and no_std. Basically you get the standard function with one of them, I wont say which. We are going to working with no_std because I can. With this we can generate a hello world to get up going.

cargo generate esp-rs/esp-template

This prompt with lots of questions but at the end you get a folder and you can run

cargo run

Library

So first off wanted a library for my gc9A01 so had to relearn rust again to get going so here is how you do it briefly

We put the lib functions is bill1.rs and bill2.rs and function exported in lib.rs.

Here is lib.rs

#![cfg_attr(not(test), no_std)]

pub mod bill1;

pub mod bill2;

Here is bill1.rs

use esp_println::println;

pub fn test_function1() {

println!("test_function 1");

}

And we can now use this in bill-test, main.rs

#![no_std]

#![no_main]

extern crate alloc;

use core::mem::MaybeUninit;

use esp_backtrace as _;

use esp_println::println;

use hal::{clock::ClockControl, peripherals::Peripherals, prelude::*, Delay};

use billlib::bill1;

#[global_allocator]

static ALLOCATOR: esp_alloc::EspHeap = esp_alloc::EspHeap::empty();

fn init_heap() {

const HEAP_SIZE: usize = 32 * 1024;

static mut HEAP: MaybeUninit<[u8; HEAP_SIZE]> = MaybeUninit::uninit();

unsafe {

ALLOCATOR.init(HEAP.as_mut_ptr() as *mut u8, HEAP_SIZE);

}

}

#[entry]

fn main() -> ! {

init_heap();

let peripherals = Peripherals::take();

let system = peripherals.SYSTEM.split();

let clocks = ClockControl::max(system.clock_control).freeze();

let mut delay = Delay::new(&clocks);

// setup logger

// To change the log_level change the env section in .cargo/config.toml

// or remove it and set ESP_LOGLEVEL manually before running cargo run

// this requires a clean rebuild because of https://github.com/rust-lang/cargo/issues/10358

esp_println::logger::init_logger_from_env();

log::info!("Logger is setup");

bill1::test_function1();

// println!("Hello world!");

loop {

println!("Loop...");

delay.delay_ms(500u32);

}

}

Debugging Again

Got my esp-prog out and managed get it going again but another hour lost. The basics seem to work. Here is the command, the same as above

. ~/esp/esp-idf/export.sh

cd ~/.espressif/tools/openocd-esp32/v0.12.0-esp32-20230921/openocd-esp32/

bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg

When running openocd this is a working output.

iwiseman@oliver:~/.espressif/tools/openocd-esp32/v0.12.0-esp32-20230921/openocd-esp32$ bin/openocd -s share/openocd/scripts -f interface/ftdi/esp32_devkitj_v1.cfg -f board/esp-wroom-32.cfg

Open On-Chip Debugger v0.12.0-esp32-20230921 (2023-09-21-13:41)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

adapter speed: 20000 kHz

WARNING: boards/esp-wroom-32.cfg is deprecated, and may be removed in a future release.

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : ftdi: if you experience problems at higher adapter clocks, try the command "ftdi tdo_sample_edge falling"

Info : clock speed 20000 kHz

Info : JTAG tap: esp32.cpu0 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : JTAG tap: esp32.cpu1 tap/device found: 0x120034e5 (mfg: 0x272 (Tensilica), part: 0x2003, ver: 0x1)

Info : starting gdb server for esp32.cpu0 on 3333

Info : Listening on port 3333 for gdb connections

Info : [esp32.cpu0] Target halted, PC=0x400D5547, debug_reason=00000001

Info : [esp32.cpu0] Reset cause (3) - (Software core reset)

Info : Set GDB target to 'esp32.cpu0'

Info : [esp32.cpu1] Target halted, PC=0x4008466A, debug_reason=00000000

Info : [esp32.cpu1] Reset cause (14) - (CPU1 reset by CPU0)For vscode I copied the examples using ctrl-p Show Example Projects and copied the hello world. The produced a launch.json

{

"version": "0.2.0",

"configurations": [

{

"type": "espidf",

"name": "Launch",

"request": "launch"

}

]

}