Verilog Language: Difference between revisions

Jump to navigation

Jump to search

| Line 11: | Line 11: | ||

This is where the outputs are a simple function of the inputs. (Sounds like pure functions | This is where the outputs are a simple function of the inputs. (Sounds like pure functions | ||

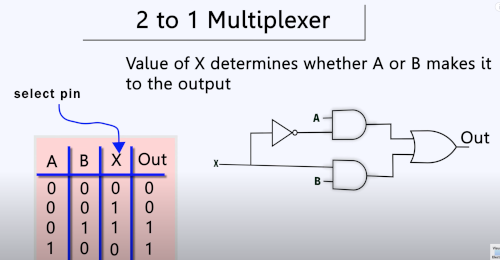

==2 to 1 Multiplexer== | ==2 to 1 Multiplexer== | ||

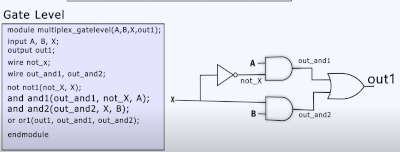

==Gate Level== | |||

This was quite useful as I have some knowledge of gates and boolean logic so it starts to make a bit of sense in verilog. Here is the truth table for the 2 to 1 multiplexer<br> | This was quite useful as I have some knowledge of gates and boolean logic so it starts to make a bit of sense in verilog. Here is the truth table for the 2 to 1 multiplexer<br> | ||

[[File:Verilog example1a.png| 400px]]<br> | [[File:Verilog example1a.png| 400px]]<br> | ||

Revision as of 06:22, 17 December 2024

Introduction

This page is meant to help understand how to approach the language. There are three levels of abstraction.

Way to describe Hardware

- Gate Level

- Dataflow Level

- Behavioral Level

Types of Logic

- Combinational Logic

- Sequential Logic

Combinational Logic

This is where the outputs are a simple function of the inputs. (Sounds like pure functions

2 to 1 Multiplexer

Gate Level

This was quite useful as I have some knowledge of gates and boolean logic so it starts to make a bit of sense in verilog. Here is the truth table for the 2 to 1 multiplexer

To model this at the gate level we could do this

Sequential Logic

Sequential logic uses memory and state