ESP32

Introduction

As the little grey cells get older probably time to give to pointers to myself

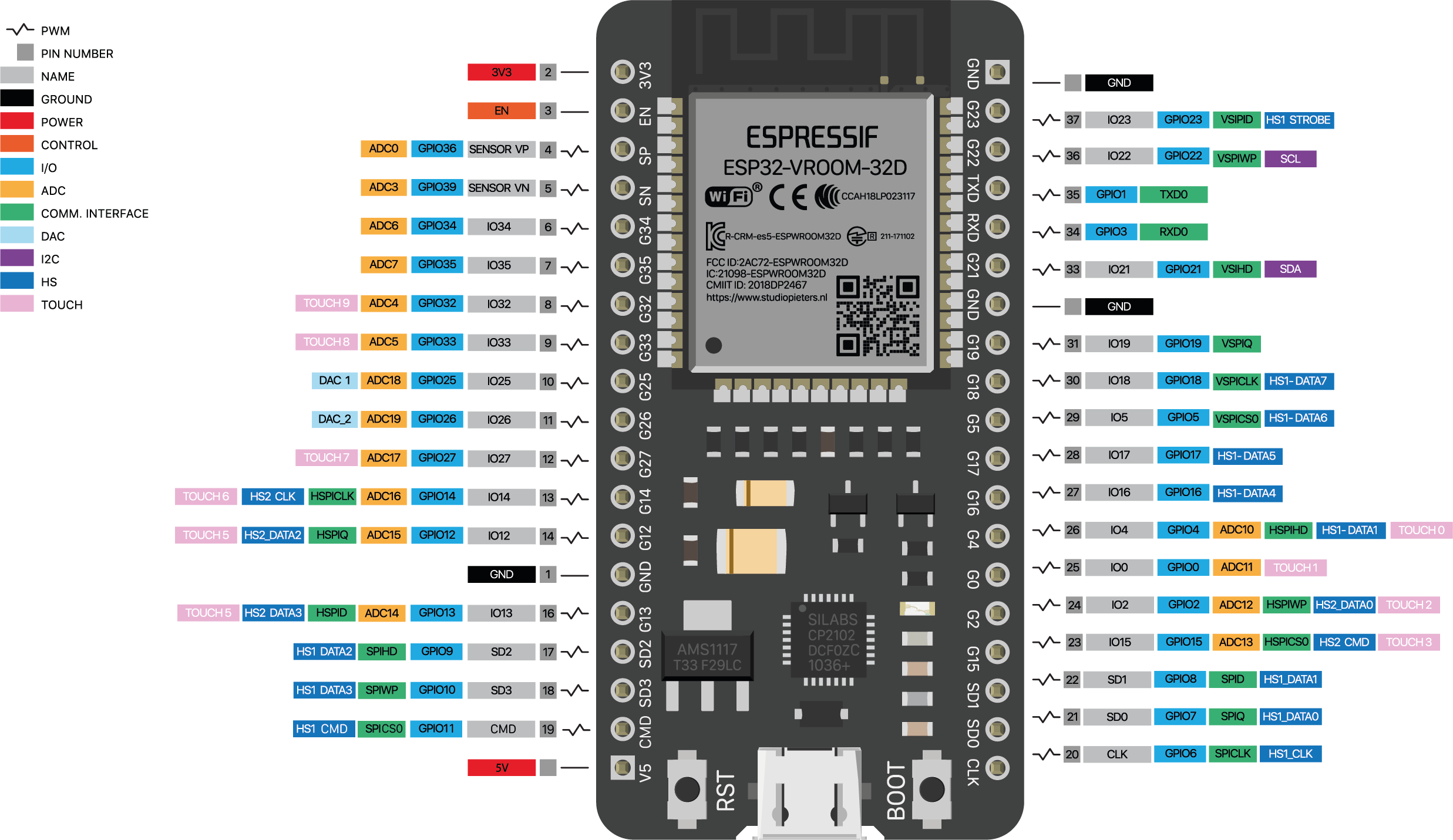

Pinout for ESP32

This is the pinout for my ESP32

UDEV

To make sure the device is recogised we need to add rules to /etc/udev/rules.d/

This is my board and my UART interface. The plugdev is the important bit as we need to not run things as root for some strange reason.

ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6001", MODE="660", GROUP="plugdev", TAG+="uaccess"

ATTRS{idVendor}=="10c4", ATTRS{idProduct}=="ea60", MODE="660", GROUP="plugdev", TAG+="uaccess"openocd and FT232R

Openocd User Manual

This can be found [here]

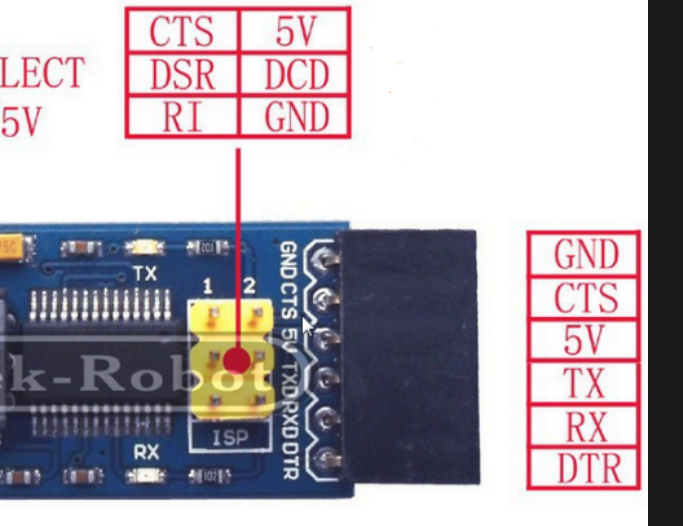

FT232

This is what I believe my FT232 is [here]

The connector shown for a similar board gives

Connecting

The following was suggested to get the JTAG interface to work.

GPIO15=TDO

GPIO12=TDI

GPIO13=TCK

GPIO14=TMS

GND=GND

ft232r.cfg

This is what I have used for ft232.cfg

interface ft232r

adapter_khz 3000

ft232r_tck_num TXD

ft232r_tdi_num RXD

ft232r_tdo_num RI

ft232r_tms_num CTS

ft232r_trst_num DTR

ft232r_srst_num DCDRunning Open OCD

The scripts are written in TCL. Here is the command to run

cd ~/.espressif/tools/openocd-esp32/v0.10.0-esp32-20210401/openocd-esp32/bin

./openocd -d3 -f ../share/openocd/scripts/interface/ft232r.cfg -f ../share/openocd/scripts/board/esp-wroom-32.cfg

Distilled Script

I have worked through the scripts provided with openocd and this is the script I believe is run from the above command.

interface ft232r

#ft232r_restore_serial 0x15

ft232r_tdi_num TXD

ft232r_tck_num DTR

ft232r_tdo_num RXD

ft232r_tms_num CTS

# trst/srst are not used but must have different values than above

ft232r_trst_num DCD

ft232r_srst_num RI

#reset_config none

adapter_khz 500

set ESP32_FLASH_VOLTAGE 3.3

# ESP_COMMON.CFG

set _FLASH_SIZE "auto"

puts "==== FLASH_SIZE $_FLASH_SIZE"

set _SEMIHOST_BASEDIR "."

puts "==== SEMIHOST_BASEDIR $_SEMIHOST_BASEDIR"

###

### configure_esp_workarea

###

proc configure_esp_workarea { TGT CODE_ADDR CODE_SZ DATA_ADDR DATA_SZ } {

#WARNING: be careful when selecting working ares for code and data, they should not overlap due to ESP32 physical memory mappings

$TGT configure -work-area-phys $CODE_ADDR -work-area-virt $CODE_ADDR -work-area-size $CODE_SZ -work-area-backup 1

# since ESP32 cannot use single address space for code and data we need additional working area to keep data

$TGT configure -alt-work-area-phys $DATA_ADDR -alt-work-area-virt $DATA_ADDR -alt-work-area-size $DATA_SZ -alt-work-area-backup 1

}

###

### configure_esp_workarea

###

proc configure_esp_flash_bank { TGT DRV SIZE } {

set _SIZE SIZE

# special value for flash driver

set _SIZE 0

# whole flash for programming purposes

# TODO: remove it when support for GDB's 'load' comand is implemented

flash bank $TGT.flash $DRV 0x0 $_SIZE 0 0 $TGT

# So define mapped flash regions as separate flashes

# OOCD creates memory map using registered flash banks

flash bank $TGT.irom $DRV 0x0 0 0 0 $TGT

flash bank $TGT.drom $DRV 0x0 0 0 0 $TGT

}

# ESP32.cfg

# The ESP32 only supports JTAG.

# transport select jtag

# Target specific registers

set EFUSE_BLK0_RDATA1_REG 0x3ff5A004

set _CHIPNAME esp32

puts "==== CHIPNAME $_CHIPNAME"

set _CPUTAPID 0x120034e5

puts "==== CPUTAPID $_CPUTAPID"

set _ONLYCPU 3

puts "==== ONLYCPU $_ONLYCPU"

set _FLASH_VOLTAGE $ESP32_FLASH_VOLTAGE

puts "==== FLASH_VOLTAGE $_FLASH_VOLTAGE"

set _CPU0NAME cpu0

set _CPU1NAME cpu1

set _TARGETNAME_0 $_CHIPNAME.$_CPU0NAME

set _TARGETNAME_1 $_CHIPNAME.$_CPU1NAME

set _RTOS "FreeRTOS"

puts "==== RTOS $_RTOS"

jtag newtap $_CHIPNAME $_CPU0NAME -irlen 5 -expected-id $_CPUTAPID

jtag newtap $_CHIPNAME $_CPU1NAME -irlen 5 -expected-id $_CPUTAPID

target create $_TARGETNAME_0 $_CHIPNAME -endian little -chain-position $_TARGETNAME_0 -coreid 0 -rtos $_RTOS

configure_esp_workarea $_TARGETNAME_0 0x40090000 0x3400 0x3FFC0000 0x10000

configure_esp_flash_bank $_TARGETNAME_0 $_CHIPNAME $_FLASH_SIZE

# APP-CPU

target create $_TARGETNAME_1 $_CHIPNAME -endian little -chain-position $_TARGETNAME_1 -coreid 1 -rtos $_RTOS

configure_esp_flash_bank $_TARGETNAME_1 $_CHIPNAME $_FLASH_SIZE

target smp $_TARGETNAME_0 $_TARGETNAME_1

$_TARGETNAME_0 esp32 flashbootstrap $_FLASH_VOLTAGE

$_TARGETNAME_0 xtensa maskisr on

$_TARGETNAME_0 xtensa smpbreak BreakIn BreakOut

$_TARGETNAME_0 esp semihost_basedir $_SEMIHOST_BASEDIR

$_TARGETNAME_1 configure -event gdb-attach {

$_TARGETNAME_1 xtensa smpbreak BreakIn BreakOut

# necessary to auto-probe flash bank when GDB is connected

halt

}

puts "==================================== Scooby doo 1"