Verilog: Difference between revisions

Jump to navigation

Jump to search

| Line 2: | Line 2: | ||

Dipping my toe into this now I own an fpga | Dipping my toe into this now I own an fpga | ||

=Hello World= | =Hello World= | ||

This is the first program. There are two files to get it to work, a pcf file which defines things you use in the verilog file. Currently my understanding is it maps hardware to names which you can reference in the verilog file. Here is the project. I only use two buttons in the example but there are four shown for the second example | This is the first program. There are two files to get it to work, a pcf file which defines things you use in the verilog file. Currently my understanding is it maps hardware to names which you can reference in the verilog file. Here is the project. I only use two buttons in the example but there are four shown for the second example<br> | ||

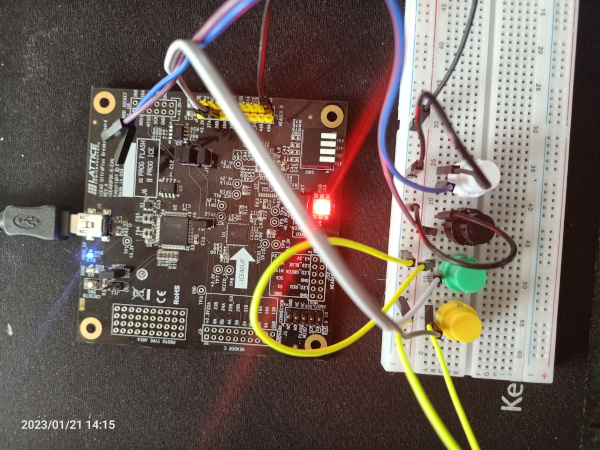

[[File:Verilog1.jpg]] | [[File:Verilog1.jpg]] | ||

==PCF Physical Constraints File== | ==PCF Physical Constraints File== | ||

Revision as of 01:19, 21 January 2023

Introduction

Dipping my toe into this now I own an fpga

Hello World

This is the first program. There are two files to get it to work, a pcf file which defines things you use in the verilog file. Currently my understanding is it maps hardware to names which you can reference in the verilog file. Here is the project. I only use two buttons in the example but there are four shown for the second example

PCF Physical Constraints File

Could not find a lexer but here we define names to io pins. You lookup the pin in the datasheet, in my case a ice40UP5K-B-EVN and you assign a name.

#LED

set_io led_0 41

#HEADER B I/O

set_io -pullup yes pmod_0 23

set_io -pullup yes pmod_1 25

Here is my first program, it defines two input buttons and 1 LED in a module called and_gate. The value of LED is true when pmod_0 and pmod_1 are true.

module and_gate (

// inputs

input pmod_0,

input pmod_1,

// Outputs

output led_0

);

assign led_0 = ~pmod_0 & ~pmod_1;

endmodule